ShBoom (1988..)

FRISC 3 - 32-х разрядный процессор, оптимизированный для выполнения языка Форт. "3" говорит о двух предыдущих прототипах стек-процессора. В основе FRISC 3 лежит однотактное выполнение Форт примитивов в среде управления в реальном масштабе времени. JHU/APL разработал FRISC 3 для удовлетворения своих потребностей в быстром Форт-процессоре для управления процессами в экспериментах на спутниках и Космическом корабле Спейс Шаттл.

Корни проекта FRISC 3 можно проследить до JHU/APL HUT проекта - секционированного

процессора, оптимизированного под язык Форт. После завершения HUT процессора,

по заказу проектной группы JHU были изготовлены прототипы 32-х разрядного

Форт-процессора по 4.0 микронной технологии кремний-на-сапфире (FRISC 1)

и 3-х микронная обьемная КМОП версия (FRISC 2). Версия FRISC 3 - коммерческий

процессор, являющийся отголоском их более ранних работ.

Silicon Composers, Inc. приобрел

коммерческие промышленные права на FRISC 3, и переименовал проект в

SC32.

Архитектура

Стеки данных и возвратов выполнены идентично, как циклические буфера

из шестнадцати 32-х разрядных ячеек, четыре из которых доступны непосредственно.

Особенностью является введение дополнительной логики, следящей за переполнением

и исчерпанием стека и автоматически производящей захват основной памяти

и обмен в этом случае. Этот стековый кеш не похож на обычный кеш данных

или команд, потому что не производит ассоциативного поиска рассеянных областей

памяти.

АЛУ читает с вершины стека данных и одного из четырех верхних элементов и пишет нв вершину. Сдвигатель на выходе АЛУ может сдвигать данные на один разряд.

В старших трех битах 32-х разрядной команды FRISC 3 содержится тип команды:

тип --- 000.. Вызов подпрограммы 001.. Ветвление 010.. Условное ветвление 011.. АЛУ и Сдвиги 100.. Чтение из памяти 101.. Сохранение... 110.. Загрузка младшей части адреса 111.. Загрузка старшей части...Особенности

FRISC 4

На Рочестерской конференции 1992 года есть упоминание о новом проекте,

как развитии SC32. В него включена поддержка целочисленного умножения и

деления, манипуляции битами, плавающая арифметика, UART, контроллер прерываний,

bootROM. Выполненный по 0.7 микрон технологии FRISC 4 работает на частоте

33 МГц.

О дальнейших развитиях проекта я не знаю...

После представления CPU/32, Harris Semiconductor лицензировал патентные права на проект и производство RTX 32P. RTX 32P - точная копия CPU/32, только с использованием пары 2.5 микронных полузаказных интегральных схем для размещения схемы проекта на одной печатной плате. RTX 32P выполняет программы на 8 MHz в типичных рабочих условиях. Harris назвал проект RTX 4000 [3], как 32-х разрядный член семейства продуктов Экспрессов Реального Времени (RTX). RTX 4000 должен был стать 32-х разрядным стек-процессором, оптимизированным для прикладных программ управления в реальном времени, подобно RTX 2000.

Планировалось, что RTX 4000 будет одночиповой промышленной версией RTX 32P, с реальными усовершенствованиями проекта. Эти усовершенствования должны были повысить быстродействие по крайней мере до 18 MHz в коммерческой версии на 2.0 микронной технологии, и до 25 MHz на 1.2 микронной технологии.

Особенности

RTX 4000 базируется на 0 операндной модели вычислений с 2 стеками,

очень близкой Форт виртуальной машине. Он способен выполнять команды, соответствующие

командам RTX 2000 при соответствующем наборе микропрограмм, и может иметь

другие, не RTX 2000 возможности, с прямой поддержкой других языков высокого

уровня типа C.

RTX 4000 оптимизирован для двухтактного обращения к памяти программ. Это сделано с пониманием того факта, что встраиваемые системы реального времени часто не могут предоставить экзотическую технологию, поддерживающую однотактное обращение к памяти на высоких скоростях. Для ускорения выполнения программ RTX 4000 выполняет обработку двух кодов операции или кода операции и вызов/возврат подпрограммы для каждой выборки команды. Для большинства команд это даёт однотактное выполнение. Особенностью RTX 4000 является применение ОЗУ микропрограмм c полем команды 9 бит, и переопределение микропрограмм пользователем.

Предполагалось несколько вариантов в семействе RTX4000, включая RTX 4002 (чип, разработанный для бетта-тестирования, вероятно по 2.0 микронной технологии), RTX 4000 (1.2 микронный чип с модулем плавающей запятой и большим количеством периферийных устройств на - чипе), RTX 4001 ( 1.2 микронный чип меньшей стоимости без модуля с плавающей запятой). Начиная с RTX 4000, в разработках используется метод со стандартной ячейкой, новые версии процессора для специализированных прикладных областей удобны и экономичны. RTX 4002 планировалось выпустить в 1989.

Harris Semiconductor и на этот раз, похоже, подвел тех, кто на него надеялся. О дальнейших успехах RTX 4000 я не слышал ...

ShBoom (1988..) |

|

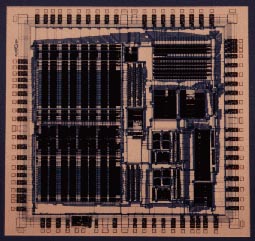

ShBoom - простой, быстрый и маленький 32-х разрядный микропроцессор, с двухстековой архитектурой. На 100МГц он выполняет одну инструкцию за такт, без нормального кеша данных и команд. Байтовые инструкции загружаются группами по четыре (32-бит), и последовательно выполняются. Процессор имеет на кристалле два 32-х разрядных стека по 16 вложений, контроллер динамической памяти и сопроцессор ввода/вывода. Уникально решена проблема загрузки констант. ShBoom загружает одиночные байты данных, идущие справа за инструкцией в текущей группе.

В 1995 году фирма Patriot Scientific приобрела права на эту разработку и анонсировала ShBoom как процессор языка Java. Хотя этот процессор не выполняет непосредственно Java байт-код, но его инструкции тоже байтовой длины и Java байт-код может быть очень близко перетранслирован к естественным инструкциям ShBoom. В добавление к этому Java-VM как и Forth-VM это стековая виртуальная машина.

Идеи, заложенные в этот процессор, себя оправдали, получился действительно быстрый и дешевый процессор, который является хорошей основой для языков высокого уровня Forth, C, Java

На сегодняшний день Patriot Scientific выпустила две модели:

PSC 1000 - 0.8 um 90, 100 МГц @ 5В

PSC 1005 - 0.5 um 90, 100 МГц @ 3.3В

Фирма возлагает большие надежды на ShBoom, а мы - на нее.